SystemVerilog Analysis Engine

The central part of Edaphic Studio is it's built-in SystemVerilog analysis engine. This engine scans your project to understand hierarchies and connections as well as analyzes your code as you type. Think of it as a fast, continuously updating compiler that doesn't rely on any external tools.

Error checking as you type!

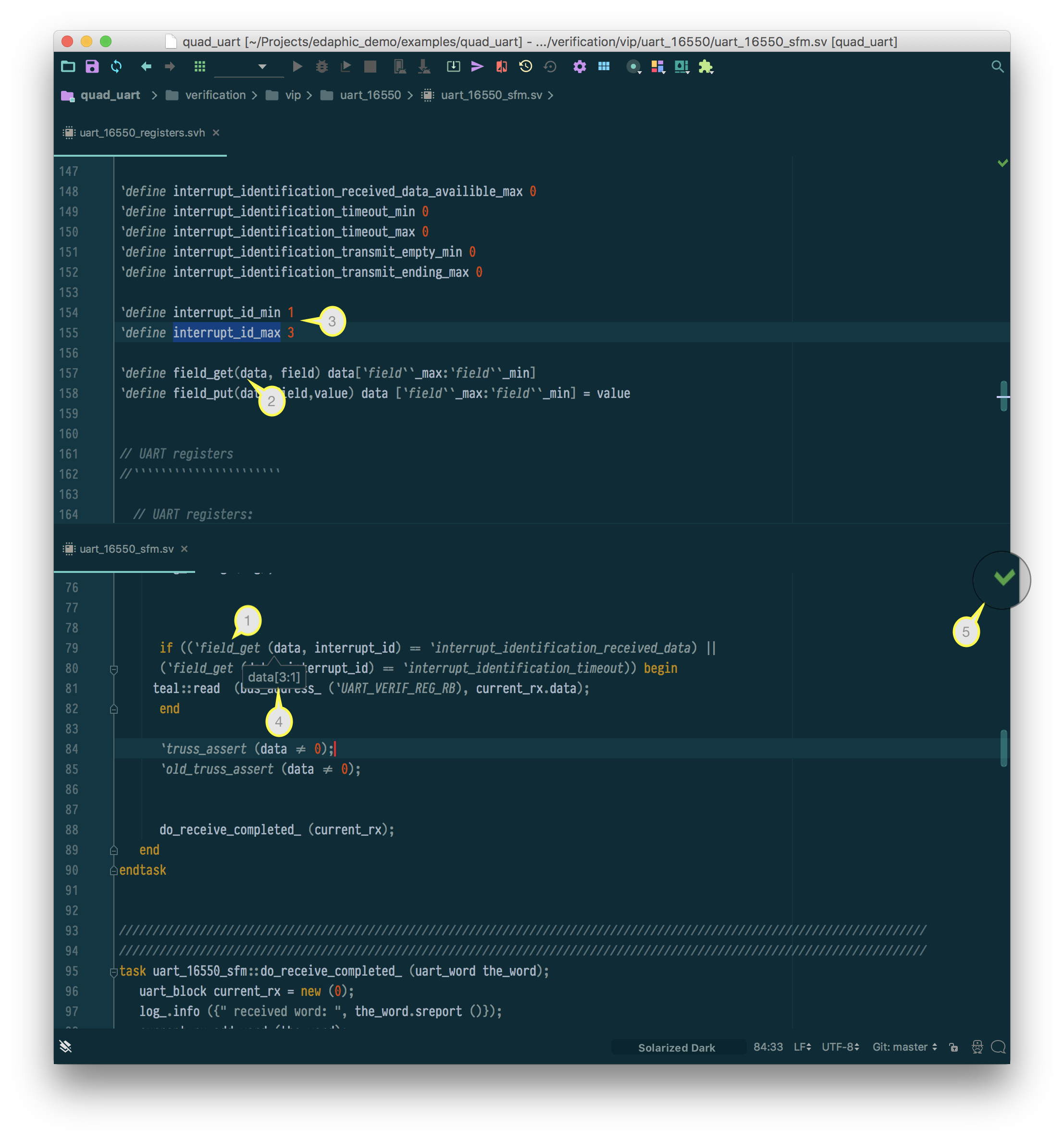

The engine works relentlessly, every time a file is modified the result is re-analyzed. Just look at the upper right corner of any opened file to see it's current status. A green check-mark and all is good, a red exclamation-point and you have errors, and yellow streak indicates warnings.

Streamline the compile & fix errors cycle!

Our goal with this engine is to cut down drastically on the slow SystemVerilog compile and fix errors cycle. A green check-mark should mean your code will compile and link. We are not fully there yet, but we are working on it, and the errors and warnings we detect already make a meaningful difference. With your support, we will make this engine more capable.

Supports all of SystemVerilog - including macros!

The engine supports the full SystemVerilog syntax today including Compiler Directives like define, macros and conditional code. It translates all macro usages into the resulting structure before doing the analysis. This Compiler Directive support allows Edaphic Studio to understand the actual intent and report errors and warnings for even complex code scenarios.

Clicking on the image to the right will take you to a page detailing how the Analysis engine works with Compiler Directives.

This code analysis is done on-the-fly and without relying on any external tools. It just works on all platforms.

Understands hierarchies and scope

The engine further builds up a hierarchical understanding of your project, which means it understands how classes, packages, and modules interconnect. This level of knowledge allows for easy code navigation, proper code completion.